PPI 8255

8255 adalah chip Programmable Peripheral Interface, berfungsi untuk antar muka paralel dengan perilaku dapat diatur dengan program. PPI 8255 terdiri dari tiga port I/O 8 bit yaitu: Port A, Port B, dan Port

Gambar Diagram blok PPI 8255

PPI 8255 memiliki Buffer bus data dua arah, yang berarti dapat berfungsi baik sebagai port input maupun port output. Arah aliran data dapat dijelaskan menggunakan pengaturan logika Read/Write. Secara mudah dapat diuraikan dengan tabel berikut:

PPI 8255 bekerja dalam tiga mode, yaitu:

1. Mode 0: Port A, Port B, dan Port sedangkan Port

Gambar Diagram Operasi PPI 8255 Mode 0

2. Mode 1: Port A, Port B bekerja sebagai port I/O dengan jabat tangan menggunakan sebagian dari pena Port C. Saluran PC0, PC1, dan PC2 berfungsi sebagai saluran jabat tangan untuk Port B sedangkan Port A menggunakan saluran PC3, PC4, dan PC5 sebagai sinyal jabat tangan. PC6 dan PC7 dapat digunakan untuk saluran I/O. Diagram operasi 8255 pada mode 1 digambarkan pada Gambar.

Gambar Diagram Operasi PPI 8255 Mode 1

3. Modus 2: Hanya Port A dapat dibuat sebagai port I/O dua arah dengan jabat tangan. Port A dapat digunakan sebagai port untuk transfer data dua arah dengan jabat tangan. Ini artinya data dapat masuk atau keluar dari saluran yang sama. Mode ini mengembangkan sistem saluran (bus) ke mikroprosesor atau mentransfer byte data ke dan dari floppy disk controller. Pada mode 2 saluran PC3 sampai PC7 digunakan sebagai saluran jabat tangan untuk Port A. Bentuk operasi 8255 sebagai mode 2 digambarkan pada diagram Gambar.

Gambar Diagram Operasi PPI 8255 Mode 2

Penyusunan dan Pengiriman Control Word

Gambar 12a digunakan untuk menformat Control Word berdasar pada mode kerja. Sedangkan gambar 25b digunakan untuk menformat Control Word untuk Port

I/O Serial

I/O serial adalah unit masukan keluaran yang bekerja atas dasar prinsip urut/seri. Dalam hal ini diperlukan proses konversi dari data paralel ke bentuk serial. Ada

· Teknik perangkat lunak

· Teknik perangkat keras.

I/O Serial Perangkat Lunak

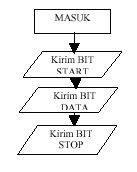

Serialisasi dan deserialisasi suatu data diselenggarakan oleh suatu perangkat program. Pada masukan program menunggu sampai menerima suatu bit start, kemudian membaca bit data. Pada keluaran program mengirim suatu urutan bit demi bit. Diagram alir program I/O serial ditunjukkan pada gambar berikut.

Gambar Diagram Alir Program I/O Serial

Prinsip utama serialisasi adalah merakit data 8 bit (atau lebih) di akumulator dan menggeser keluar bit demi bit pada frekuensi tertentu. Cara yang sederhana adalah mengeluarkan isi akumulator ke salah satu saluran dari port I/O (Port 0). Akumulator kemudian digeser ke kanan satu bit, diimplemen suatu tunda dan bit selanjutnya dikeluarkan sampai semua bit data paralel dikeluarkan.

Sebaliknya deserialisasi dilakukan dengan membaca bit 0 dan merekamnya ke akumulator. Akumulator di geser kekiri satu posisi dengan tunda tertentu. Kemudian bit 0 dibaca lagi dan dilakukan proses pencatatan dan penggeseran akumulator sampai data byte terselesaikan.

Keuntungan I/O terprogram terletak pada ketersederhanaannya dan tidak perlu harus menyiapkan perangkan keras. Kelemahannya terletak pada masalah waktu yaitu lambatnya proses.

I/O Serial Perangkat Keras

Salah satu komponen LSI standar adalah Universal Asynchronous Receiver-Transmitter (UART). UART bekerja mengubah data serial ke paralel dan data paralel ke serial. UART paling sering digunakan untuk ope rasi kecepatan rendah ke sedang. Sedangkan untuk transmisi kecepatan tinggi digunakan jenis Universal Synchronous Receiver Transmitter (USRT).

Fungsi UART adalah pada pengubahan serial–paralel. Prinsip pengubahan serial ke paralel dilukiskan pada gambar berikut:

Gambar Pengubahan Serial ke Paralel

Dua fungsi pokok UART adalah:

· Mengambil data paralel dan mengubah menjadi arus bit serial dengan diawali bit start, bit data, bit paritas, dan karakter penghenti.

· Mengambil arus bit serial dan mengubahnya menjadi bit paralel.

Sebuah UART standar mempunyai tiga seksi yaitu: sebuah penerima, sebuah pengirim, dan sebuah seksi pengendali.

Gambar Diagram UART

UART memerlukan baik port masukan maupun port keluaran untuk perantaraan dengan sistem mikroprosesor. Dua diantara piranti UART adalah:

· MC 8650 Asynchronous Comunication Interface Adaptor (ACIA) dari Motorolla.

· 8251 Universal Synchronous and Asynchronous Receiver Transmitter (USART) dari Intel.

Motorolla 6850 ACIA

6850 tersusun dari sejumlah register serial paralel masukan keluaran dan rangkaian pengendali standar EIA RS 232. Diagram blok ACIA digambarkan seperti Gambar 16.

Gambar Diagram blok 6850 ACIA

Penghantaran 6850 pada saluran/bus dari sistem dapat digambarkan seperti Gambar 17. Data serial yang masuk dan keluar adalah sinyal kompatibel TTL dan harus di bufer untuk memberikan tingkatan yang diperlukan untuk menggerakkan alat-alat serial.

Gambar Penghantaran 6850 pada Saluran / Bus

Intel 8251 USART

8251 dirancang oleh Intel yang memiliki pasilitas sebagai UART dan juga USRT. Dengan kata lain 8251 dapat dipakai baik sebagai alat tak serempak maupun alat serempak. Sehingga 8251 diberi nama USART. 8251 menyediakan pasilitas pengiriman dan penerimaan data sinkron dan tak sinkron. Organisasi logika 8251 ditunjukkan pada Gambar 18.

Gambar Diagram Logika 8251

Metode Pengendalian I/O

Pengaturan alih data dari alat luar dengan sistem komputer/sistem mikroprosesor menerapkan suatu strategi penjadwalan. Pada pengendalian alat I/O dikenal adanya tiga metode yaitu:

· Metode Polling

· Metode Interupsi

· Metode Akses Memori Langsung (AML)

Metode Polling

Metode polling merupakan metode pengendalian I/O melalui program. Semua pengalihan data dari dan ke alat I/O diselengarakan oleh program. Prosesor mengirim dan meminta data sepenuhnya dibawah kendali program. Pengalihan data dapat dilaksanakan baik melalui mekanisme jabat tangan maupun tanpa jabat tangan. Dalam mekanisme jabat tangan isyarat diperiksa secara terus menerus. Program terus menerus berputar lewat sejumlah pengetesan untuk menentukan apakah masukan atau keluaran dapat diselenggarakan pelayanannya atau tidak. Bila ditemukan alat yang memerlukan pelayanan, rutin pelayanan diaktifkan dan pemilihan saluran diproses. Gambar 19. menunjukkan diagram alir pengendalian I/O dengan metode polling. Metode polling adalah metode pengendalian I/O yang paling sederhana dan paling umum digunakan. Metode ini tidak memerlukan perangkat keras khusus dan semua pengalihan I/O dikendalikan oleh program. Pengalihan semacam ini disebut pengalihan serempak dengan program.

Gambar Diagram Alir Pengendalian I/O Sistem Polling

Metode Interupsi

Pengendalian I/O dengan metode polling mempunyai dua kelemahan :

· Pemborosan waktu prosesor karena status semua periferal diperiksa terus menerus secara berurutan.

· Karena harus memeriksa status semua alat I/O maka waktu kerjanya menjadi lambat. Ini merupakan kelemahan dalam sistem waktu nyata (Real Time), dimana satu periferal mengharap layanan dalam satu waktu tertentu.

Kelemahan ini diatasi dengan menggunakan layanan waktu tak sinkron menggunakan interupsi. Tiap alat I/O atau pengendalinya dihubungkan ke sebuah saluran interupsi. Saluran interupsi menggerbangkan sebuah permintaan interupsi ke Mikroprosesor. Bilamana sebuah alat I/O memerlukan layanan , alat akan membangkitkan pulsa interupsi atau status suatu tingkatan saluran untuk menarik perhatian mikroprosesor. Mikroprosesor akan memberikan layanan pada alat I/O jika ada interupsi dan jika tidak ada interupsi mikroprosesor melakukan instruksi selanjutnya. Logika pengendalian I/O dengan metode interupsi ditunjukkan pada diagram alir Gambar .

Gambar Diagram Alir Logika Pengendalian I/O Metode Interupsi

Begitu permintaan interupsi diterima dan disetujui oleh Mikroprosesor, alat I/O harus dilayani. Untuk melayani alat I/O, maka Mikroprosesor melaksanakan suatu routin pelayanan khusus. Ada

· Bagaimana status program yang dilaksanakan pada Mikroprosesor pada saat interupsi harus diperilahara dalam stack.

· Bagaimana mikroprosesor dapat mengenali secara tepat alat I/O mana yang membangkitkan interupsi. Identifikasi ini dapat dilakukan dengan perangkat keras, perangkat lunak, atau kombinasi perangkat keras dan perangkat lunak. Pencabangan ke alamat alat I/O disebut Pemvektoran Interupsi. Rutin perangkat lunak menetapkan identitas alat yang meminta layanan interupsi. Rutin identifikasi interupsi akan memilih saluran setiap alat yang dihubungkan dengan sistem. Setelah dikenal alat mana yang mencetuskan interupsi maka ia kemudian bercabang ke alamat rutin penanganan interupsi yang sesuai. Metode ke dua yang digerakkan oleh perangkat lunak, tetapi dengan pertolongan beberapa perangkat keras tambahan. Metode ini menggunakan rantai beranting (Daisy Chain) untuk mengenal alat yang mencetuskan interupsi. Metode tercepat adalah interupsi yang divektorkan. Adalah menjadi tanggung jawab pengendali alat I/O untuk memberikan baik interupsi maupun pengenal alat yang menyebabkan interupsi atau lebih baik lagi alamat pencabangan bagi rutin penanganan interupsi. Bila pengendali hanya memberikan pengenal alat, adalah tugas perangkat lunak mencari tabel alamat pencabangan bagi tiap alat. Ini sederhana bagi perangkat keras tapi tak mencapai performansi tertinggi.

· Prioritas

Beberapa interupsi dapat dibangkitkan serentak. Mikroprosesor diberi tugas untuk memutuskan bagaimana urutan pelayanannya. Setiap alat diberikan suatu prioritas. Mikroprosesor melayani setiap alat sesuai prioritasnya. Dalam dunia komputer prioritas 0, menurut konvensi memiliki prioritas. tertinggi, prioritas 1 yang kedua demikian seterusnya. Prioritas dapat diset baik pada perangkat keras maupun perangkat lunak. Pengaturan prioritas dengan perangkat keras dikerjakan oleh suatu piranti yang disebut Programmable Interrupt Controller (PIC). Struktur dasar logika PIC dapat digambarkan seperti Gambar 21.

Gambar 21. Struktur Dasar Logika PIC

Akses Memori Langsung

Interupsi menjamin tanggapan yang paling cepat dari proses pengendalian data pada I/O. Akan tetapi pelayanan pada alat masih diselenggarakan oleh perangkat lunak. Kecepatan Transfer paralel sebuah Mikroprosesor dibatasi oleh Overhead perangkat lunak yang terlibat dalam pengiriman kata-kata berurutan. Ini mungkin masih tidak cukup cepat bagi pengolahan yang melibatkan alih memori cepat. Kembali disini menggantikan perangkat lunak dengan perangkat keras. Rutin perangkat lunak yang menyelenggarakan alih data antara memori dengan alat I/O

digantikan oleh prosesor perangkat keras khusus yang disebut dengan Direct Memory Access Controller (DMAC). Sebuah DMAC adalah prosesor khusus yang dirancang untuk menyelenggarakan alih data berkecepatan tinggi antara memori dengan alat luar. Dalam akses memori langsung digunakan dua teknik untuk berhubungan dengan memori:

· Prosesor dihentikan atau ditangguhkan oleh DMAC. DMAC memegang pengendalian bus dan membiarkan alat I/O berhubungan langsung dengan memori.

· DMAC mencuri satu siklus memori dari mikroprosesor, memberinya kepada pengiriman data antara memori dan alat I/O.

DMAC adalah prosesor khusus yang memutuskan hubungan atau mengisolasi MPU dari bus-bus dan mengatur pengiriman yang diperlukan antara memori dan alat I/O. Gambar 22. menunjukkan diagram blok kerja DMAC.

Gambar Diagram Blok Kerja DMAC

Pada saat sistim bekerja, saklar pada posisi atas sehingga saluran terhubung dari mikroprosesor ke sistem memori dan peripheral. Untuk membaca file ke disk diperlukan sejumlah perintah ke Disk Controller, memerintahkan untuk mencari dan membaca blok data yang dari disk. Jika Disk Controller telah menemukan byte pertama dari blok data, disk Controller mengirim sinyal DMA Request (DREQ) ke DMAC. Jika DMAC tidak dalam terhalang maka DMAC mengirim sinyal hold request (HRQ) ke mikroprosesor melalui pin HOLD. Mikroprosesor menanggapi masukan ini dengan mengambangkan saluran/bus dan mengirim sinyal hold Acknowledge (HLDA) ke DMAC. Jika DMAC menerima sinyal HLDA, akan mengirim sinyal untuk menghubungkan bus/saluran ke posisi DMAC.

Pada saat DMAC mengontrol saluran, ia mengirim alamat memori dimana byte pertama dari disk controller di tulis. Selanjutnya DMAC mengirim sinyal DMA acknowledge (DACK) ke disk controller untuk memberitahukan kesiapan mengeluarkan byte. Akhirnya DMAC mengaktifkan saluran MEMW* dan IOR* pada saluran kontrol.

1 komentar:

info yang sangat membantu..

moga menjadi amal soleh

kunjungi jg bahan bacaan saya :

jurnal ekonomi andalas

Posting Komentar